컴퓨터구조

[컴퓨터구조] 램, CPU

파송송

2022. 11. 17. 14:40

728x90

램 RAM,

- Random Access Memory

- = 주기억장치, = 무작위 접근 메모리

- 기억된 정보 읽기와 다른 정보를 기억하는 메모리로 응용 프로그램의 일시적 로딩, 데이터의 일시적 저장 등에 사용되는 컴퓨터 부품

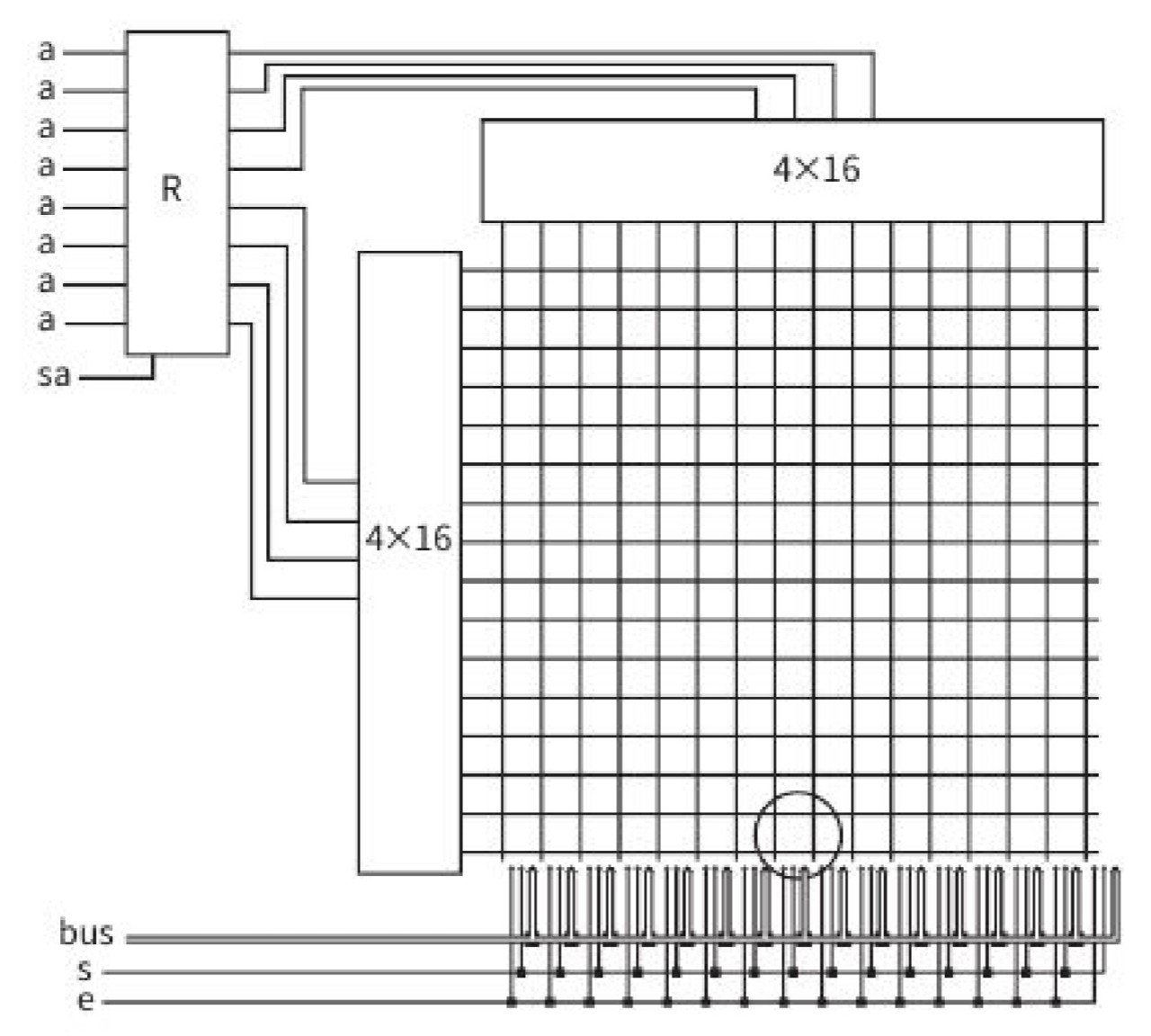

- 게이트, 레지스터, 디코더를 사용하여 저장소를 만들 수 있음

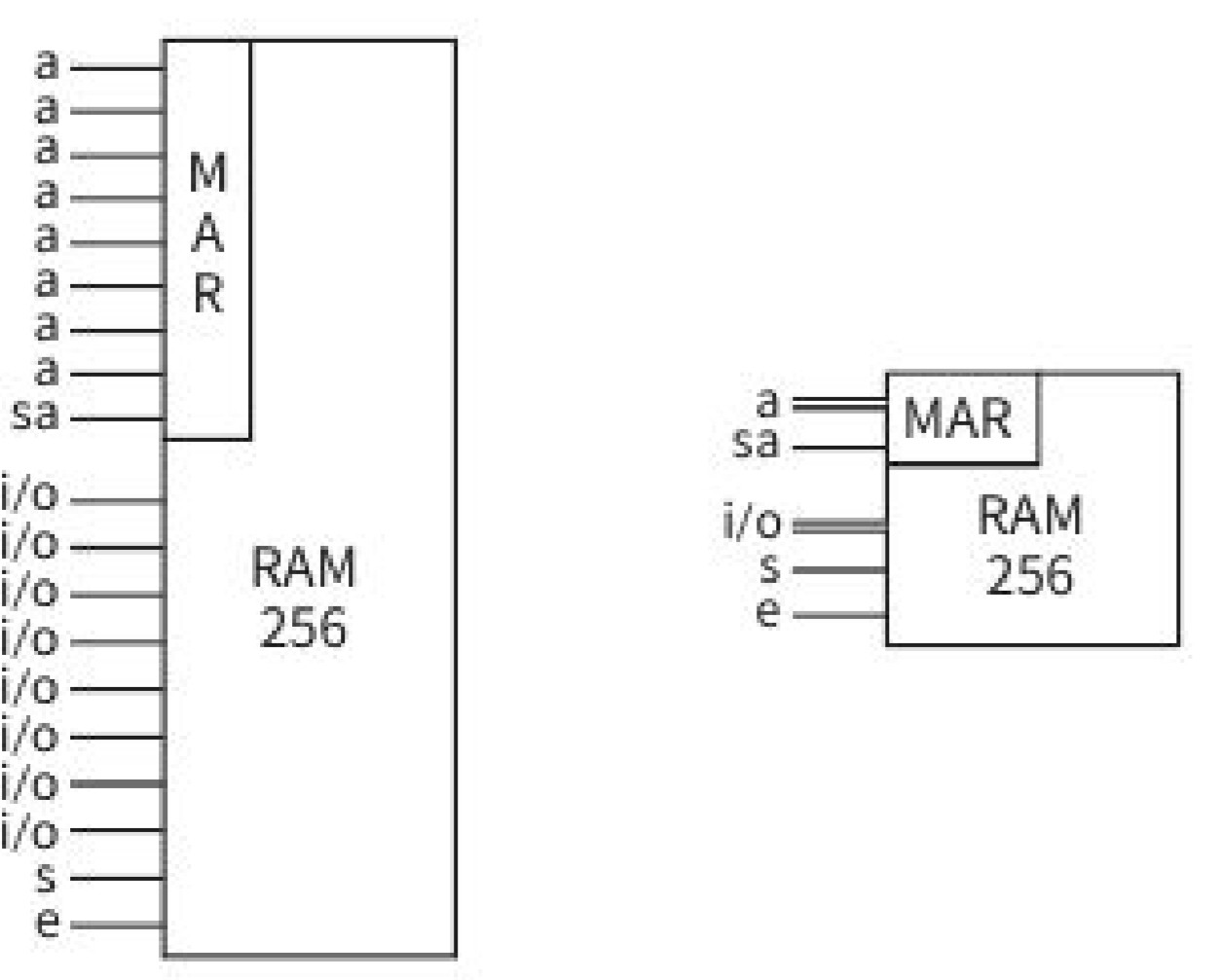

- a: 다른 장치에서 내보낸 바이트가 버스를 통해 들어오는 입구

- sa: 버스를 통해 들어온 바이트를 레지스터 넣고 싶을 때 1, 아닐 때 0 상태로 둔다

- 비트 패턴과 일치하는 디코더 1개만 선택됨.

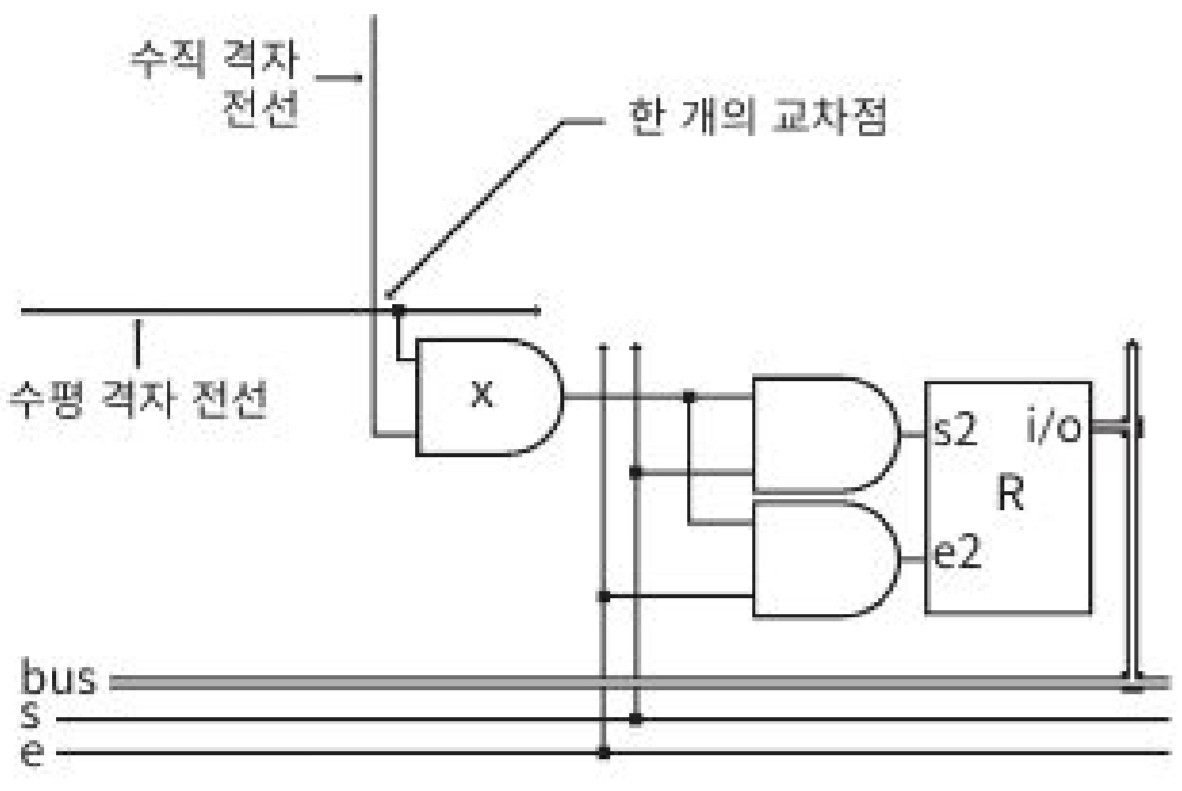

- 16 x 16 = 256개의 교차점이 생기고 수직 디코더, 수평 디코더의 입력을 각각 하나씩 받아 1개의 교차점에 들어있는 바이트에 접근함

- 256개의 교차점이 있지만 수평, 수직 디코더는 하나의 1만 내보내기에 1개만 1, 255개는 0인 상태이다

- x는 격자에 연결된 유일한 부품이고 나머지는 bus. s. e에 연결되어 있음

- 257개의 레지스터가 존재

- 256개는 바이트 저장하는데 사용

- 1개는 위치를 가리키는데 사용함 -> MAR (Memory Address Register)

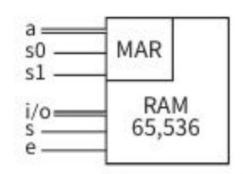

램 용량 키우기

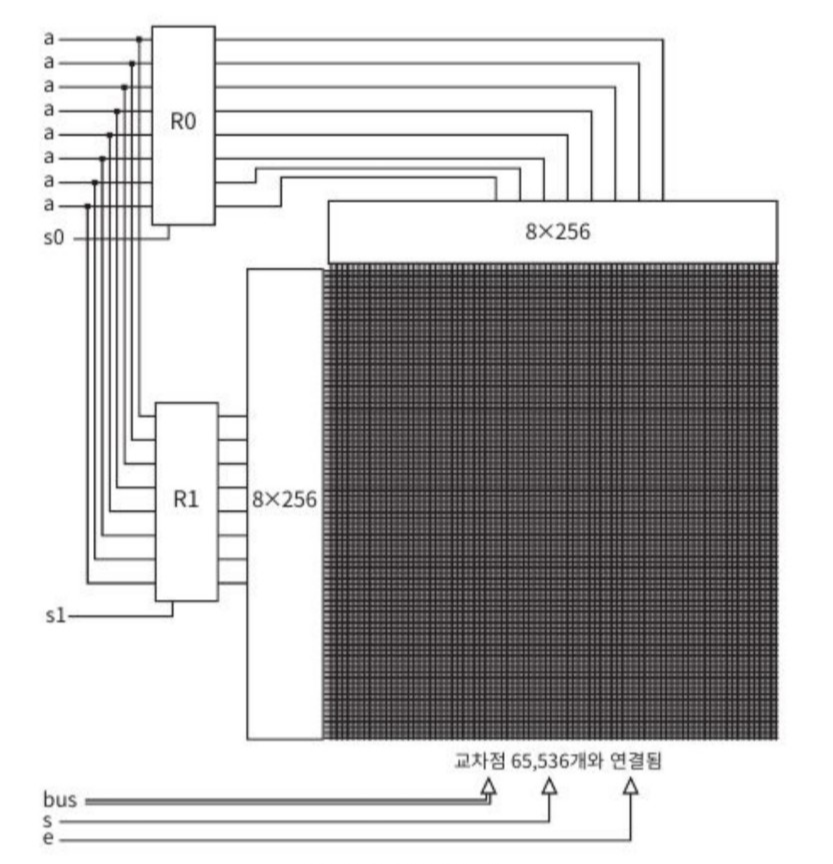

- 용량을 키우기 위해서는 MAR구조 부터 변경해야함 (레지스터 1개 -> 레지스터 2개, 많으면 많을수록 많은 더 많은 주소를 가리킴)

- 위에서는 레지스터 1개를 사용하여 4개의 출력을 4x16 디코더를 사용하여 256개의 메모리 주소를 가졌음

- 레지스터 2개를 사용하여 8개의 출력을 8x256 디코더를 이용하여 65,536개의 메모리 주소를 가지게 만들 수 있음

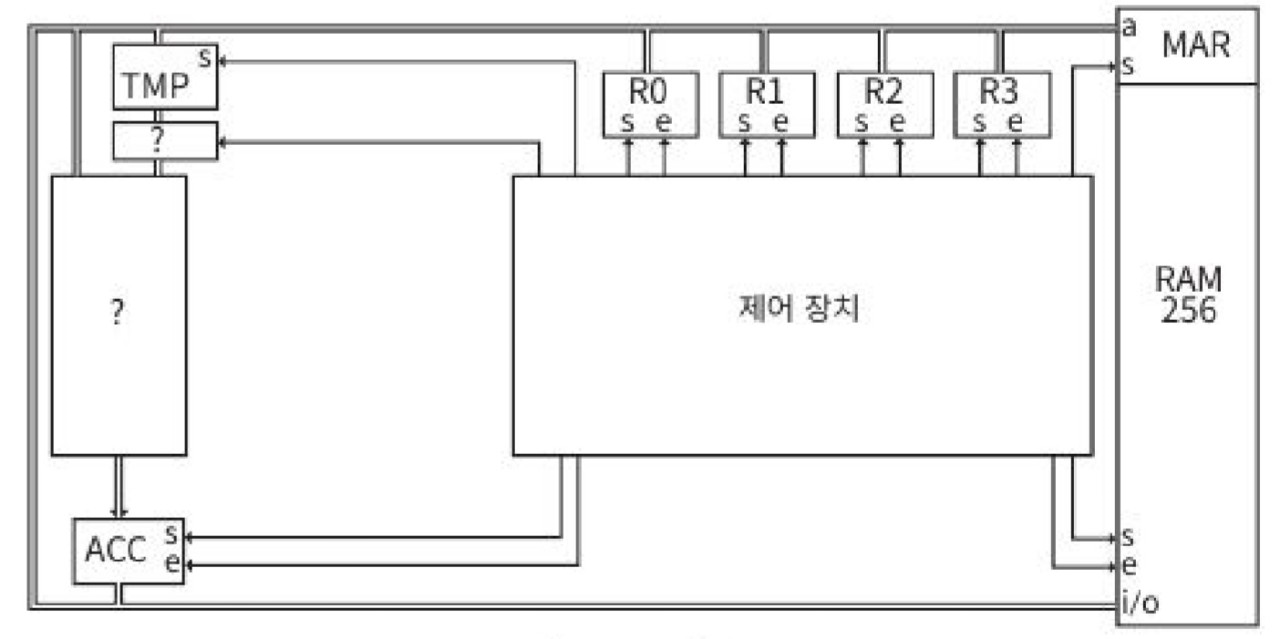

CPU Central Processing Unit

- PC의 여러 장치들의 행동을 제어하고 통제하는 것

- = 중앙 처리 장치

- 바이트를 처리하는 장치

- 제어장치는 CPU와 램 안에 들어있는 입력 제어 단자 s와 출력 제어 단자 e에 들어오는 비트를 0이나 1로 만들어서 입력과 출력을 통제하는 장치

- R0, R1, R2, R3는 단기 기억용 레지스터(범용 레지스터)로 CPU가 어떤 인을 수행하는 데 필요한 바이트를 임시로 기억하는 용도로 쓰임

- TMP는 임시 레지스터로 버스를 통해 들어오는 바이트를 일시적으로 기억하는 용도

- 입력 제어 단자 s를 1로 만들어주면 버스를 통해 바이트가 TMP로 설정됨과 동시에 ?의 입력 단자로 들어감

- 입력 제어 단자를 0으로 바꿔 입력을 멈춰도 출력은 멈추지 않음(s가 있지만 e가 없음)

- ACC는 누산기로 ?에서 나오는 바이트 하나를 일시적으로 저장하는 장치이며 ACC에 들어 있는 바이트 데이터는 버스로 출력되어 다른 부품에 입력으로 들어간다.

728x90